## Requirements for high-speed spectroscopy using L3CCDs Vik Dhillon & Tom Marsh, 10 February 2006

## 1 Introduction

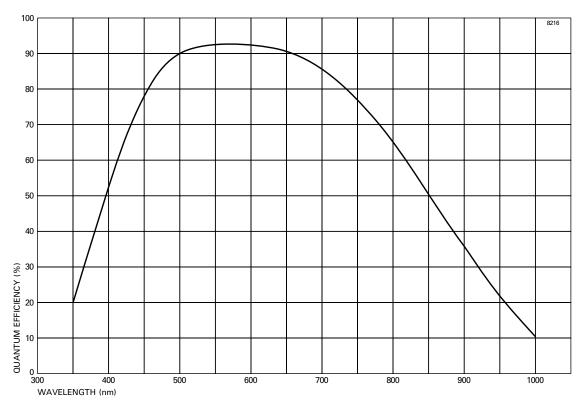

This document describes the functional and performance requirements for a high-speed spectroscopic camera used for high-time resolution astrophysics. The combination of high-speed and spectroscopy means that detector noise is a more important issue than it is for high-speed imaging (e.g. with ULTRACAM). Low-light-level CCDs (L3CCDs<sup>1</sup>) appear to have ideal properties for high-speed spectroscopy, combining all of the advantages of CCDs (i.e. high QE, large formats) with low detector noise, achieved using significant on-chip gain.

To investigate whether L3CCDs are suited to high-speed astronomical spectroscopy, a consortium from the Universities of Sheffield, Warwick and the UKATC, Edinburgh were awarded 180 000 Euros as part of OPTICON JRA3. Our aims are to procure a suitable L3CCD device, mount it in a cryostat, add L3CCD functionality to the ULTRACAM hardware and software, and characterise the resulting camera for high-speed spectroscopy both in the lab and on the sky.

The project began in earnest in early 2005, when we assessed the available L3CCD devices on the market and decided to procure the E2V CCD201 – see the JRA3 2005 interim report for details. A data sheet for the device is given in Appendix B. The device is currently being mounted in an ESO cryostat and, alongside this, we have had to design and build a series of high-voltage clock driver boards for the SDSU CCD controller. This board should be of use to any observatory currently using these controllers who wish to read out L3CCDs. We expect the project to move from the lab to the telescope at the end of 2006, where we will perform our on-sky tests using the EFOSC2 spectrograph mounted on the ESO 3.6-m telescope at La Silla.

## 2 Requirements

We shall be performing the on-sky tests of the L3CCD camera on the EFOSC2 spectrograph, for which the most useful grisms are:

- Grism 3:  $\Delta \lambda = 9.7$ Å and 1331Å coverage (e.g. 3800–5100Å).

- Grism 7:  $\Delta \lambda = 6.2$ Å and 852Å coverage (e.g. 4250–5100Å).

- Grism 14: Similar to 7, but with  $\Delta \lambda = 5.8$ Å, giving ~400 km/s velocity resolution at 4500Å.

The efficiencies of all these grisms are  ${\sim}20{-}30\%$  in the wavelength range of interest.

Running the EFOSC2 exposure time calculator gives 15 e<sup>-</sup>/pixel/s (in total, across the spatial profile) for a 15th-magnitude A-star using grism 14. Each CCD201 pixel will subtend 0.136 arcsec spatially, hence we will get approximately 2.4 e<sup>-</sup>/pixel/s at peak in 0.8 arcsec seeing. So, to maintain <0.2 e<sup>-</sup>/pixel (i.e. a safe count rate as far as linearity is concerned, see Appendix A), we'll need a frame rate of approximately of 12 Hz.

<sup>&</sup>lt;sup>1</sup>The generic name for the technology is actually Electron Multiplying CCDs (EMCCDs). L3CCD and Impactron are the names given to the EMCCDs made by E2V and Texas Instruments, respectively.

The above calculation tells us that we will need to frame the L3CCD at faster than 10 Hz in order to be able to photon count on  $\sim$ 15th-magnitude stars. If this is not achievable, we will have to increase the magnitude limit, below which we will not be able to photon count. Note, however, that there is no need to read out the entire array at this rate – a window of 100×1024 pixels (i.e. 13.6 arcseconds) should suffice to record the target and sky, and this can be further reduced by binning spatially by a factor of at least 2.

We summarise the theory of operation of L3CCDs in Appendix A. Based on this, and the calculations given above, we have arrived at the following functional and performance requirements, all of which refer to both the unit gain output and the EM gain output of the CCD201.

- Frame rate: As described above, we have a frame rate requirement of 10 Hz for 1 x 1000 x 100 windows. As a goal, we would like to read out 2 x 1000 x 100 windows at 100 Hz. This would enable us to observe 13th magnitude stars at the 3.6m with grism 14.

- Windows: Two different window modes are required: First, a single-window mode for the highest speeds/brightest targets, or when the target and/or comparison star are very close to each other. Second, a two-window mode, one for the target and the other for a comparison star. The windows must have variable xsize and ysize, be separated in y, and be non-overlapping. Both windows can have the same xstart, xsize and binning factors. The ysize needs to be set independently for each window.

- **Binning:** Binning is required in both x and y. The x and y values can be different, but the same values can be used for each window. xbinning values of 1,2,4,8 and ybinning of 1,2,4,8 are required at a minimum. It isn't clear if binning will be an advantage when using high gain this will depend on where the clock-induced charge is produced and if you can read out twice as quickly if binning by 2. It would still be useful, however, to bin to reduce the quantity of data and when using the unit gain output, so this is a requirement.

- Drift mode: Analagous to the drift mode in ULTRACAM, this mode will allow windows to be stacked up in the masked area of the chip, thereby reducing the vertical clocking time and hence increasing the frame rate. The difference with spectroscopy is that we will often be using 2 windows, in which case the rows between the windows will have to be dumped to maximise speed. The requirement is therefore to implement drift mode for 1 window, with a goal of implementing it for 2 spatially-separated windows, if feasible.

- Other readout modes: In addition to the drift mode, one-window mode and twowindow modes described above, none of which involve clearing the chip between frames, we will also require a full-frame with clear mode (to set arbitrarily short exposure times for calibration frames), a full-frame with overscan mode (for testing purposes), a full frame with no clear (for the best duty cycle), and one-window mode with clearing (for more efficient observing with the shortest exposure times).

- **SDSU-PCI card accumulation:** The SDSU-PCI card must have a threshold facility, where it outputs 0 for no photons and 1 for a photon. The threshold level must be user-definable and will be calculated by the existing ULTRACAM GUI from the readout noise and gain settings and then passed through the xml header system to the SDSU-PCI card.

It must also be possible to turn thresholding off for testing purposes, and a flag saying whether it is off or on should also be passed through the xml header system.

It is also a requirement that data frames can be accumulated in blocks in the SDSU-PCI card, where the number of frames in each block can be set by the user on the existing ULTRACAM GUI and passed through the xml header system. This accumulation must happen after the thresholding, and each block must be timestamped.

- **Exposure times:** The system should allow a maximum exposure time of 3600 seconds and a minimum exposure time of 10 millisecond.

- **Timestamping:** Absolute timing to 1 millisecond is required, using the same GPS system as is used in ULTRACAM.

- **Readout noise:** The readout noise in L3CCD mode must be less than 1/50 of the gain in photon-counting mode.

- Dark current: The dark current must be less than 0.001 e<sup>-</sup>/pixel/s.

- **Clock-induced charge:** It is difficult to give a precise figure here, as the detailed behaviour of CIC is still unknown. Suffice it to say that CIC must be minimised!

- **Readout speeds:** At least two readout speed (i.e. ADC pixel rate) settings are required, e.g. one slow, low readout noise setting, and one fast, high readout noise setting.

- File headers: The xml file headers must record all the variable parameters listed above and have a version number/date.

- Data format: Unformatted binary, as in the present ULTRACAM system, but only one channel's worth. The xml headers must have a unique identifier saying that we are using the L3CCD (and not ULTRACAM). The GPS timestamps must be written in the same way that they are in ULTRACAM.

- Alignment: Assuming that ESO align their chips within the cryostat so that the centre of the slit corresponds to the centre of the chip, then we must ensure that the centre of the image area of the CCD201, not the frame-transfer border of the chip, is located at the centre of the cryostat. Before doing this, however, we must first check with Peter Sinclaire (ESO, La Silla) that our assumption is correct.

## A Theory of EMCCDs

## B Data sheet for CCD201

### L3 CCD Simulation

#### T.R. Marsh

October 28, 2005

#### 1 Introduction

The purpose of this document is to detail the mathematics of the statistics of the avalanche readouts of L3 CCDs with the purpose of investigating how they can be simulated. Only a little of the stuff here is original, but some of the background is not laid out in an easily accessible form in the papers I have read, so I thought it would help to have everything in one place. It is rather mathematical and if you prefer not to plough through all the (many) equations, then you may just want to look at the figures and take a look at section 6 which summarises the main points.

#### 2 The Model

In the avalanche gain section of the L3 CCD, high clock voltage causes there to be a significant probability that an electron will produce another electron when moving from stage to stage. In common with others, I will call this probability p. In practice it is fairly small, of order 0.015. However there are many such multiplication stages and so the overall gain can be large.

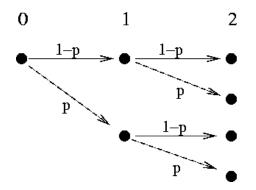

A schematic of the process is shown in Fig. 1. The key thing to note is that at any stage if there are, say, n electrons, then each of them independently goes through the same multiplication process for the next stage. i.e. it is not the case that if there are 100 electrons that there is a p chance at the next stage that there will be 200 (instead it will be  $p^{100}$ ).

#### 3 Statistics

Key properties of interest are the mean gain as a result of a given number r stages of this process, the

Figure 1: Schematic of the multiplication process, starting from 1 electron on the left at stage 0. At stage 1, a second electron is created with probability p. Each of the two possible electrons at stage 2 then independently can go through the same multiplication, so that as many as four electrons may be present by stage 2.

variance of the gain which is important because it is a measure of the noise added by the avalanche process, and, in most detail of all, the probability distribution of the gain. This was worked out by Matsuo et al (1985) although they do refer to difficult-to-access texts for several results; I will repeat their analysis here which is based upon a general theory of "branching processes" which goes under the name Galston-Watson branching process, which was first considered in the context of extinctions of populations in the 19th century. I do this fairly fully so that this document is self-contained.

#### 3.1 Fundamentals

First I will assume that we start from one electron at stage 0. I am interested in the distribution at stage r, which I will associate with a random variable called  $N_r$ . The probabilities we want are  $P(N_r = n)$ . For instance these give us the mean

gain after r stages  $g_r$  from

$$g_r = E(N_r) = \sum_{n=0}^{\infty} P(N_r = n)n,$$

(1)

where I use the standard notation E(X) to mean the "expected value" of a random variable X. However, it turns out that it is not possible to obtain a simple expression for the probabilities except in special cases, and we have to adopt a more sophisticated approach. To do so we will consider two functions known as the "moment generating function"  $\mu$  (MGF) and the "probability generating function"  $\pi$  (PGF) which for a random variable N are defined by

$$\mu_N(t) = E(e^{tN}) = \sum_{n=0}^{\infty} P(N=n)e^{tn}, \quad (2)$$

and

$$\pi_N(t) = E(t^N) = \sum_{n=0}^{\infty} P(N=n)t^n, \qquad (3)$$

These two functions are closely related to each other as it is easily seen that

$$\pi_N(t) = \mu_N(\ln t). \tag{4}$$

If one takes the derivative of the MGF then

$$\frac{d\mu_N(t)}{dt} = E(Ne^{tN}),\tag{5}$$

and therefore

$$\left. \frac{d\mu_N(t)}{dt} \right|_{t=0} = E(N),\tag{6}$$

which is the first moment (mean) of N that we want. It is then obvious that

$$E(N^p) = \left. \frac{d^p \mu(t)}{dt^p} \right|_{t=0},\tag{7}$$

and hence the term "moment generating function". The idea is that sometimes the moment generating function is easier to handle than the probability distribution and so it is possible to obtain moments when once cannot obtain (easily) the probabilities themselves. Similarly, from the definition of the PGF one can show that

$$P_N(n) = \frac{1}{n!} \left. \frac{d^n \pi_N(t)}{dt^n} \right|_{t=0},$$

(8)

and hence this is the "probability generating function".

The MGF and PGF are standard functions in statistics. A final result which we use below is that if one has two independent random variables, N and M then

$$\pi_{N+M}(t) = E(t^{N+M}),$$

(9)

$$= E(t^N)E(t^M), \qquad (10)$$

$$= \pi_N(t)\pi_M(t). \tag{11}$$

The first to the second line uses the property that for two independent random variables X and Y, E(XY) = E(X)E(Y). An identical result applies to MGFs.

#### 3.2 The PGF and MGF for avalanche multipliers

Consider the PGF at stage r + 1 of the avalanche multiplier

$$\pi_{r+1}(t) = E(t^{N_{r+1}}) \tag{12}$$

$$= \sum_{k} E(t^{N_{r+1}} | N_r = k) P(N_r = k) (13)$$

where we have written  $\mu_{N_{r+1}} = \mu_{r+1}$  etc for short. The last line introduces an expectation conditional on a particular value of  $N_r = k$  for the previous stage. This is relatively easy to calculate because if one knows that there were k electrons at stage r, then the distribution for stage r + 1 is simply the combined result of k single electron multiplications,  $(N_1)_1 + (N_1)_2 + (N_1)_3 + \ldots + (N_1)_k$  where each element is distributed as  $N_1$ , the distribution after 1 stage with a 1 - p chance of 1 electron and a p chance of 2 electrons. This has corresponding PGF (dropping the subscript 1 because we will use this special case a fair bit)

$$\pi(t) = (1-p)t + pt^2, \tag{14}$$

and thus the PGF for the combination of k such variables is, by Eq. 11,  $= \pi^k(t)$ , and therefore from Eq. 13 we have

$$\pi_{r+1}(t) = \sum_{k} P(N_r = k) \pi^k(t), \quad (15)$$

$$= \pi_r(\pi(t)). \tag{16}$$

We can immediately write from this that

$$\pi_2(t) = \pi(\pi(t)),$$

(17)

$$\pi_3(t) = \pi(\pi(\pi(t))), \tag{18}$$

$$\pi_4(t) = \pi(\pi(\pi(\pi(t)))), \quad (19)$$

etc, and also therefore that

$$\pi_{r+1}(t) = \pi(\pi_r(t))$$

(20)

$$= (1-p)\pi_r(t) + p\pi_r^2(t), \quad (21)$$

the last line following from Eq. 14. A similar relation applies to the MGF:

$$\mu_{r+1}(t) = (1-p)\mu_r(t) + p\mu_r^2(t).$$

(22)

Eqs 21 and 22 are recurrence relations that can be applied to deduce the PGF and MGF at stage rgiven that  $\pi_0(t) = t$  and  $\mu_0(t) = e^t$ . They correspond to equation 4 from Matsuo et al (1985).

#### 3.3The mean and variance

We are now in a position to deduce the mean gain, because if we take the derivative of Eq. 22 and set t = 0 then by Eq. 6 and using the fact that  $\mu(t =$ 0) = 1 for any MGF, we have

$$g_{r+1} = (1+p)g_r.$$

(23)

Given that  $g_0 = 1$  then we have

$$g_r = (1+p)^r,$$

(24)

which is what one would have hoped. To derive the variance we want the second moment, and therefore the second derivative of Eq. 22 which after setting t = 0 leads to

$$E(N_{r+1}^2) = (1+p)E(N_r^2) + 2pg_r^2.$$

(25)

Using  $\sigma^2 = E(X^2) - E(X)^2$ , leads to

$$\sigma_{r+1}^2 = (1+p)\sigma_r^2 + p(1-p)(1+p)^{2r}, \qquad (26)$$

where we have substituted the relation for  $g_r$ . Starting from  $\sigma_0 = 0$ , one can show that this recurrence relation is satisfied by

$$\sigma_r^2 = \frac{1-p}{1+p} \left( g_r^2 - g_r \right).$$

(27)

cause of the extra noise added by the avalanche gain section: the gain can be large but it is also uncertain by a similar order of magnitude. As  $p \to 1$ ,  $\sigma_r \to 0$ , reflecting the fact that if multiplication is certain, then the gain just becomes  $2^r$  with no spread. Unfortunately, this is not a realistic case in practice. The uncertainty in the gain in practice is why L3 CCDs operated in a strict proportional mode effectively have half the QE of a standard CCD.

#### 3.4The probability distribution

According to Eq. 8, to get the probability distribution we must take the n-th derivative of Eq. 21 and divide by n!. This leads to the recurrence relation

$$P_{r+1}(n) = (1-p)P_r(n) + p\sum_{k=0}^{n} P_r(k)P_r(n-k),$$

(28)

where  $P_r(n)$  is a short-hand form of  $P(N_r = k)$ . This can be computed given that  $P_r(0) = 0$  and  $P_0(1) = 1$ , however, it does not lead to analytically tractable expressions, and one must resort to computation. Computing it directly can take a long time. For example, on my desktop, taking p = 0.015 and r = 591, then g = 6629. It turns out that the probability is approximately  $\exp -x/g$ , and so in an exact computation one would be interested in numbers up to a few times q. For instance, computing up to gains of 30,000 would not be unreasonable in this case. On my workstation this takes 600 seconds, and since it is dominated by the sum in the above equation, it scales as the maximum number squared. Luckily, since the sum is a convolution, FFTs can help out, and the same computation with FFTs only takes 22 seconds which is an acceptable overhead for the start of a data simulation for instance. FFTs do have one disadvantage in this case which is that round-off errors limit how low one can go in probability, but computing in double precision gives a reliable dynamic range of  $\sim 14$  orders of magnitude which should be fine.

#### **Clock-Induced Charges** 3.5

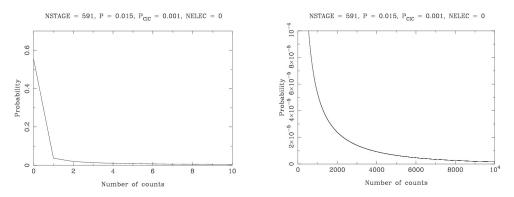

During clocking it is possible for electrons to be generated without the aid of incident photons. Nor-As  $r \to \infty$  and therefore  $g_r \to \infty$ ,  $\sigma_r/g_r \to$  mally these are buried in readout noise but in an  $\sqrt{(1-p)/(1+p)} \sim 1$  for small p. This is the root L3CCD they will be amplified and therefore be significant. Any generated in the parallel shifts will undergo precisely the same amplification as photon-generated events, and will be indistinguishable from them. Those generated in the avalanche register however will have a different distribution because if say a CIC appears in the last 10 section of the register, they will not be amplified much, and so we expect a skew towards much lower numbers of electrons. There seems to be some uncertainty over which will dominate but I have been told that it is the in register events that are most important because of the high voltages (Basden, prov. comm.). Therefore from now on I will only discuss these latter events.

The probability distribution of pure CICs can be considered in the case of no input electron. Then at each step of the avalanche register let there we a small probability  $p_{CIC}$  of an electron being generated. If this happens on step k of the total r, then it will be amplified over the next r - k steps leading to a contribution with distribution  $P_{r-k}$ . The overall contribution from step k will in fact be

$$P'_{k}(n) = (1 - p_{CIC})\delta_{0n} + p_{CIC}P_{r-k}(n)$$

(29)

and the final total distribution will be the convolution of all such distributions for k = 1 to r. Convolution once again suggests FFTs, and the calculation of the final distribution can in fact be nicely tacked on to the FFT computation of  $P_r$  at little extra computational cost. One of the nice features of these computations is that there is no "downscatter" in that the probability of a number of counts n at any stage depends only upon earlier probabilities for 0 up to n and not on any higher values. This allows an exact computation up to some preset limit.

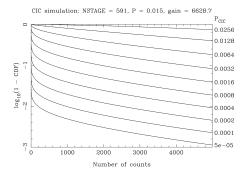

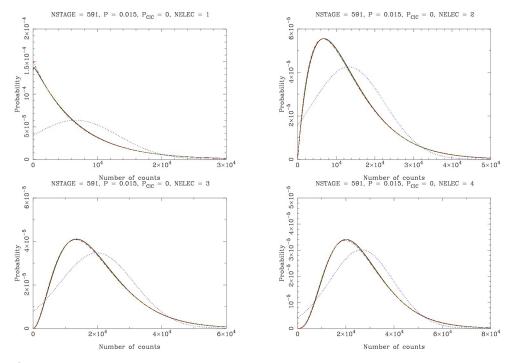

Fig. 2 shows the results of computations of CIC distributions for several different assumed values for  $p_{CIC}$ . The point about no "downscatter" is visible in the lack of "edge" effects on the right-hand side of this figure which is exactly set at the highest value considered.

In photon counting mode, one sets a threshold above which a pixels is counted as having a photon. To avoid loss of sensitivity this must be set as low as possible, but not so low that many spurious events are generated by readout noise. For example, in the case shown if Fig. 2 a level of 100 would result in only a small loss of counts (about 2%) while being

Figure 2: The logarithm of the probability of obtaining a CIC > x is plotted as a function of x for several different CIC probabilities, marked on the right, but with other parameters held fixed as indicated at the top of the plot. this shows for instance that for  $p_{CIC} =$ 0.0008, slightly fewer than 1 in 10 pixels will suffer a CIC with more than 1000 counts.

much greater than a readout noise of, say, 10 electrons RMS. However, the figure shows that it may instead be CICs that really set the threshold, depending upon  $p_{CIC}$ . For instance if  $p_{CIC} = 0.0032$ , then a threshold of 100 would see ~ 60% of pixels with spurious "photons" due to CIC. Since in photon counting mode one wants to keep the object signal well below a mean rate of 1 photon/pixel, this would be a disaster. Raising the threshold to 1000 would reduce the rate to ~ 30% but also lose 1 in 6 or so of the real counts.

For the case shown, a value for  $p_{CIC}$  in excess of  $10^{-4}$  or so will be bad news. As I understand it, the probability of CICs is a function of the voltages in the sense that increasing voltages imply increasing  $p_{CIC}$  as well as increasing gain. It may be that the increase in gain outstrips  $p_{CIC}$ , on the other hand we may find that there is some optimum gain with respect to CICs and readout noise.

At present there seems much uncertainty over a reasonable value for  $p_{CIC}$  and whether CICs in the serial register (as modelled here) dominate over parallel CICs. It may depend upon the nature of the clock waveforms. It will be important to be able to characterise CICs well in real devices. For instance by clocking out the serial register without any parallel clocks (if possible). My hope is that like readout noise in the old days of CCDs, CICs are a problem that will get better with time.

#### 3.5.1 The mean output from CICs

Since the output probability distribution of CICs is the convolution of the  $P'_k$  distributions discussed above, then the MGF of the ouput is given by

$$\mu_{CIC} = \Pi_{k=0}^{r-1} \left( 1 - p_{CIC} + p_{CIC} \mu_k \right).$$

(30)

Taking the derivative in order to compute the mean gives

$$\frac{d\mu_{CIC}}{dt} = \sum_{k=0}^{r-1} p_{CIC} \frac{d\mu_k}{dt} \Pi_{l \neq k} \left(1 - p_{CIC} + p_{CIC} \mu_k\right).$$

(31)

Setting t = 0, and remembering that  $\mu(0) = 1$  gives the mean CIC-only output to be

$$g_{CIC} = \sum_{k=0}^{r-1} p_{CIC} g_k$$

(32)

$$= p_{CIC} \sum_{k=0}^{r-1} (1+p)^k \tag{33}$$

$$= \frac{p_{CIC}}{p}(g-1), \qquad (34)$$

where  $g = (1 + p)^r$  as before. This nicely shows that it is important that  $p_{CIC} \ll p$ .

#### 4 Simulating L3 CCDs

We need the probability distributions discussed above to simulate the action of L3 CCDs. This can be done by computing the exact probabilities as outlined in the previous section and then searching a look-up table. Basden et al (2003) found that for small p and large r that the distribution for a single electron input ignoring CICs was fairly well matched by an exponential distribution of the form

$$P(x) = \frac{1}{g}e^{-x/g}.$$

(35)

I find that the following function

$$P(n) = \frac{1}{g-1} \left(\frac{g-1}{g}\right)^n, \qquad (36)$$

which has a mean of g and a variance of  $g^2 - g$  does a rather better job, especially at small g. The fact that this is not quite the exact variance of Eq. 27 is because this probability distribution is only approximate. In reality it tends to be too large for  $n \ll g$  and  $n \gg g$  and too small for  $n \sim g$ . Still, the approximation is still pretty close to the mark as far as I can determine and makes a quick way to generate the distribution to compute

$$N = \operatorname{int}\left(1 - \frac{\ln X}{\ln g/(g-1)}\right),\tag{37}$$

where X is a uniform random number between 0 and 1.

All the above holds for a single input electron. If m electrons are input then each will be independently amplified and so the resulting probability distribution will be the convolution of m of the above probability distributions. Basden et al (2003) give the following approximation for their exponential distribution:

$$Q_n(m) = \frac{m^{n-1} \exp(-m/g)}{g^n (n-1)!},$$

(38)

which gives the probability of an output of m electrons given an input of n. I use the letter Q because this probility represents the chance of an output of m given an input of n, as opposed to the previous usage of the chance of an output of n at stage r. This equation would be an approximation, even if their single electron probability was correct, but it is a pretty good one in many cases as I will show in the next section.

For my improved single electron distribution, Eq. 36, I find the following exact expression for a convolution of n such distributions:

$$Q_n(m) = \frac{(m-1)!}{(m-n)!} \frac{1}{(g-1)^n (n-1)!} \left(\frac{g-1}{g}\right)^m,$$

(39)

which applies so long as  $m \ge n$  and n > 0. For instance setting n = 1 immediately returns the single electron input case. This is still approximate since the single electron input is approximate, and at high gains at least it is indistinguishable from Basden et al's (2003) approximation, i.e. it fits the real distribution as well (or as poorly) as Basden et al. It may be possible to find a similar analytic approximation for CICs, although they are certainly not simple exponentials.

One could repeatedly instead sample the 1 electron distribution and add the results; whether this

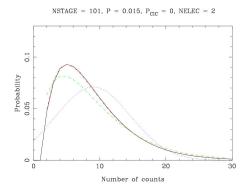

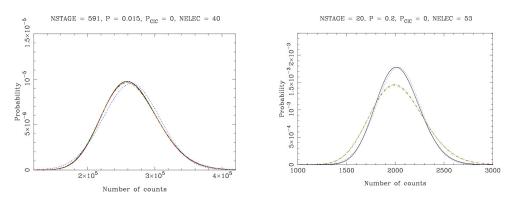

Figure 6: The probability distribution for 2 input electrons in a low gain case. This brings out the advantage of the revised approximation Eq. 39 (red dot-dash line) compared to Eq. 38 (green dashed line).

is feasible is probably a matter of computational time. The CICs can always be added in from a single lookup.

I do not yet know the practicality in terms of time of implementing look-up tables once they have been calculated. I expect them to be slow, but not unreasonably so. For example, one could look-up from a table of 65000 values in about 16 "binary chops", which does not seem too bad.

#### 5 Example Distributions

In this section I just present some example distributions in Figs. 3 to 6. Key points are

- 1. In-register CIC events have very extended tails (Fig. 3)

- 2. Basden et al's (2003) approximation for multiple input electrons is better than a gaussian of the correct mean and variance up to quite high input numbers. (Fig. 5)

#### 6 Executive summary

These are the main points to take from this work:

1. The statistics of the gain produced by L3 CCDs are somewhat complicated, but they can be calculated in a reasonable amount of time, so I hope that accurate data simulations will be possible.

- 2. At high gain the distribution given a single electron at the start of the avalanche regsister is close to exponential as in Eq. 35 and as shown in the top-left of Fig. 4.

- 3. An approximation which works somewhat better at lower gains is given in Eq. 36.

- 4. Eqs 35 and 36 have multi-electron equivalents: Eqs 38 and 39. The equations don't do well when the multiplication probability is large. Examples are shown in Figs 4 to 6.

- 5. Clock-induced charges (CICs) are potentially serious, but be very careful with any figures you see quoted for them because there is a lot of folklore/hogwash floating around about them.

- 6. CICs generated on the chip are indistinguishable from normally generated events, but might show up as a gradient in the parallel direction, with higher numbers of events the further a given pixels has had to travel.

- 7. CICs generated in the serial register can have an extremely skewed distribution with many very small events, but also a long tail extending to large counts (Fig. 3).

- 8. In photon counting mode at least CICs simply add extra background, the crucial but unknown quantity being just how much do they add.

- 9. Characterisation of CICs is important. It would be nice to be able to clock out the serial register without parallel shifts for instance because then one can determine the importance of events generated in the serial register alone.

I have written various programs to compute the distributions discussed here and can easily generate many such plots.

#### 7 References

Basden, A.G., Haniff, C., Mackay, C., 2003, MNRAS, 345, 985

Matsuo, K., Teich, M.C., Salej, B.E.A, 1985, IEEE, Transaction on electron devices, Vol. ED-32, No. 12, 1223

Figure 3: The probability distribution for 0 input electrons, i.e. pure CIC events. I show a zoomed in one on the left to show the significant chance in this case of no CIC events at all, and a larger scale one on the right to show the very extended tail of the CIC events, which is this case have a mean value of 442 despite having a 55% chance of being zero.

Figure 4: The probability distributions for 1, 2, 3 and 4 input electrons with no CICs. The green dashed line shows Basden et al (2003)'s approximation, the red dash-dotted line shows my approximation, while the blue dotted line shows a gaussian of the same mean and variance (which the distribution should tend towards by the central limit theorem). Note that the scales change on each plot.

Figure 5: The probability distribution for 40 input electrons with no CICs. The various lines are as in Fig. 4. The distribution remains significantly skewed and so the approximate expressions remain better than a gaussian even for this relatively large number of input electrons. However the right-panel shows that gaussians can be better especially when p is large.

# ezv technologies

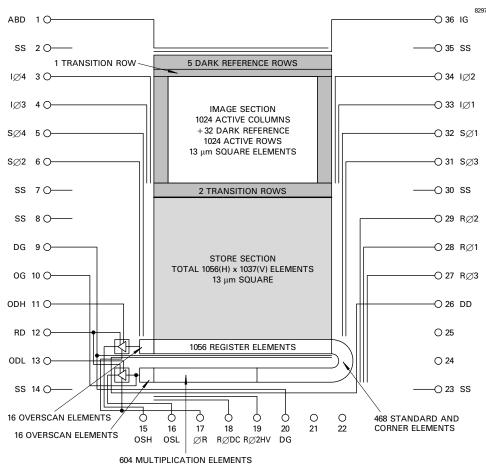

#### CCD201-20 Back Illuminated 2-Phase IMO Series Electron Multiplying CCD Sensor

#### INTRODUCTION

The CCD201 is a large format sensor (>1k<sup>2</sup>) in the L3Vision<sup>TM</sup> range of products from e2v technologies. This device uses a novel output amplifier circuit that is capable of operating at an equivalent output noise of less than one electron at pixel rates of over 15 MHz. This makes the sensor well suited for scientific imaging where the illumination is limited.

The sensor is a frame transfer device and can operate in inverted mode to suppress dark current as this is now the dominant noise source (even at high readout rate). The image and store sections are designed to operate in 2-phase mode, to maximise the highest achievable parallel transfer frequency.

The sensor functions by converting photons to charge in the image area during the integration time period, then transferring this charge through the image and store sections into the readout register. Following transfer through the readout register, the charge is multiplied in the gain register before conversion to a voltage by an output amplifier.

The sensor has two output amplifiers; a low noise, high responsivity output for normal CCD operation and a large signal amplifier for when multiplication gain is employed.

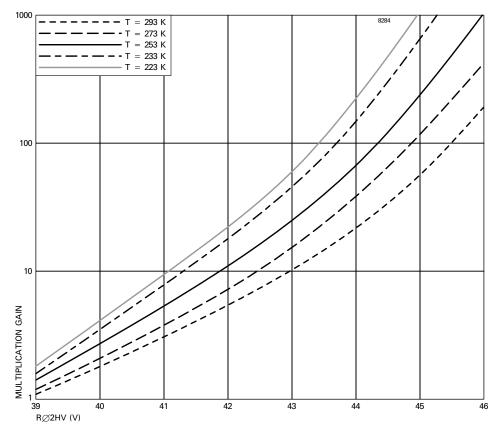

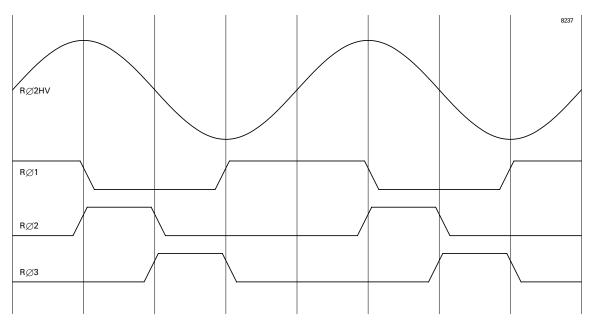

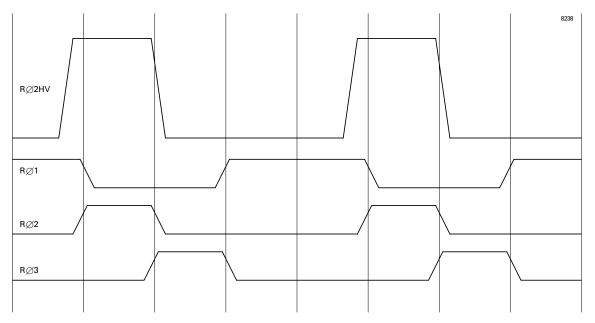

Operation of the high gain mode is controlled by adjustment of the multiplication phase amplitude RØ2HV.

#### **GENERAL DATA**

| Active image area                 | <br>. 13.3 x 13.3 mm    |

|-----------------------------------|-------------------------|

| Image section active pixels       | <br>1024 (H) x 1024 (V) |

| Image pixel size                  | <br>13 x 13 μm          |

| Number of output amplifiers       | <br>2                   |

| Fill factor                       | <br>100%                |

| Additional dark reference columns | <br>32                  |

| Additional overscan rows          | <br>8                   |

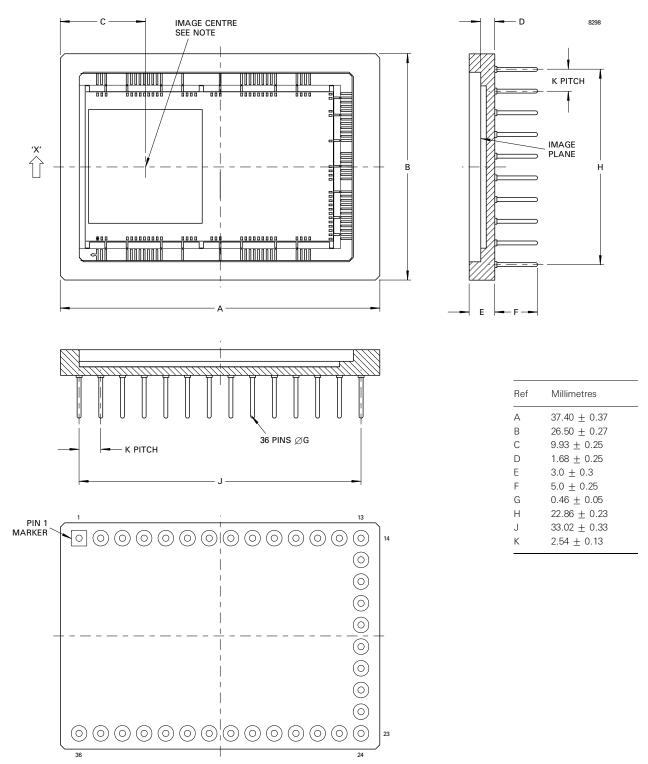

#### PACKAGE DETAILS (see Fig. 15) Ceramic Package

| Overall dimensions                    |  |  |  |  |  |  |  | 3 | 7.4 | Х | 26.5 | mm  |

|---------------------------------------|--|--|--|--|--|--|--|---|-----|---|------|-----|

| Number of pins .                      |  |  |  |  |  |  |  |   |     |   |      | 36  |

| Inter-pin spacing                     |  |  |  |  |  |  |  |   |     |   | 2.54 | mm  |

| Mounting position                     |  |  |  |  |  |  |  |   |     |   |      | any |

| The pin 1 marker is shown in Fig. 15. |  |  |  |  |  |  |  |   |     |   |      |     |

#### STORAGE AND OPERATION TEMPERATURE EXTREMES

|                              | MIN   | MAX   |

|------------------------------|-------|-------|

| Storage temperature (°C)     | -200  | + 100 |

| Operating temperature (°C)   | - 120 | + 75  |

| Temperature ramping (°C/min) | -     | 5     |

**Note:** Operation or storage in humid conditions may give rise to moisture on the sensor surface on cooling, causing irreversible damage.

e2v technologies (uk) limited, Waterhouse Lane, Chelmsford, Essex CM1 2QU, UK Telephone: +44 (0)1245 493493 Facsimile: +44 (0)1245 492492 e-mail: enquiries@e2v.com Internet: www.e2v.com Holding Company: e2v technologies plc

e2v technologies inc. 4 Westchester Plaza, PO Box 1482, Elmsford, NY10523-1482 USA Telephone: (914) 592-6050 Facsimile: (914) 592-5148 e-mail: enquiries@e2vtechnologies.us

#### **TYPICAL PERFORMANCE SPECIFICATIONS**

Except where otherwise specified, the following are measured for operation at a pixel rate of 15 MHz, with typical operating voltages. Parameters are given at 223 K unless specified otherwise. Where parameters are different in the normal and high gain mode, both are given.

| PARAMETER                                                                             | UNIT                    | MIN | TYPICAL    | MAX  |

|---------------------------------------------------------------------------------------|-------------------------|-----|------------|------|

| Output amplifier responsivity, HR amplifier (normal mode) (see note 1)                | μV/e <sup>-</sup>       | -   | 5.3        | -    |

| Output amplifier responsivity, LS amplifier (normal mode) (see note 1)                | μV/e <sup>-</sup>       | -   | 1.4        | -    |

| Multiplication register gain, LS amplifier (high gain mode)<br>(see notes 2, 3 and 4) |                         | 1   | -          | 1000 |

| Peak signal - 2-phase IMO                                                             | e <sup>-</sup> /pixel   | 50k | 80k        | -    |

| Charge handling capacity of multiplication register (see note 5)                      | e <sup>-</sup> /pixel   | -   | 730k       | -    |

| Charge handling capacity of HR amplifier (see note 6)                                 | e_                      | -   | 280k       | -    |

| Charge handling capacity of LS amplifier (see note 6)                                 | e_                      | -   | 1M         | -    |

| Readout noise at 50 kHz with CDS, HR amplifier (normal mode) (see note 6)             | e <sup>-</sup> rms      | -   | 3.1        | -    |

| Readout noise at 1 MHz with CDS, HR amplifier (normal mode) (see note 6)              | e <sup>-</sup> rms      | -   | 6.0        | -    |

| Amplifier reset noise (without CDS), HR amplifier (normal mode) (see note 6)          | e <sup>-</sup> rms      | -   | 50         | -    |

| Readout noise at 15 MHz with CDS, LS amplifier (normal mode) (see note 6)             | e <sup>-</sup> rms      | -   | 43         | -    |

| Amplifier reset noise (without CDS), LS amplifier (normal mode) (see note 6)          | e <sup>-</sup> rms      | -   | 100        | -    |

| Readout noise at 1 MHz (high gain mode) (see note 6)                                  | e <sup>-</sup> rms      | -   | <1         | -    |

| Maximum frequency (settling to 1%), HR amplifier (see notes 6 and 7)                  | MHz                     | -   | -          | 3    |

| Maximum frequency (settling to 5%), HR amplifier (see notes 6 and 7)                  | MHz                     | -   | -          | 4.5  |

| Maximum frequency (settling to 1%), LS amplifier (see note 6 and 7)                   | MHz                     | -   | -          | 13   |

| Maximum frequency (settling to 5%), LS amplifier (see note 6 and 7)                   | MHz                     | -   | -          | 20   |

| Maximum parallel transfer frequency (see note 1)                                      | MHz                     | -   | 0.9        | -    |

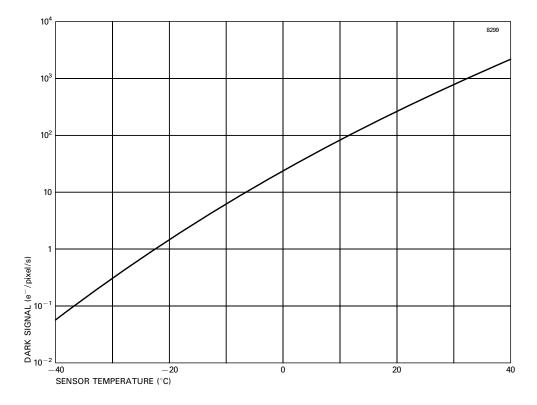

| Dark signal at 293 K (see note 8)                                                     | e <sup>-</sup> /pixel/s | -   | 260        | 530  |

| Dark signal non-uniformity (DSNU) at 293 K (see note 9)                               | e <sup>-</sup> /pixel/s | -   | 90         | -    |

| Excess noise factor (see note 10)                                                     |                         | -   | $\sqrt{2}$ | -    |

#### NOTES

- 1. Measured at a pixel rate of 1 MHz.

- 2. The typical variation of gain with RØ2HV is shown in Fig. 1.

- 3. The variation of gain with R $\emptyset$ 2HV at different temperatures is shown in Fig. 1.

- 4. Some increase of RØ2HV may be required throughout life to maintain gain performance. Adjustment of RØ2HV should be limited to the maximum specified under Operating Conditions.

- 5. When multiplication gain is used and clock timings optimised, a linear response of output signal with input signal of better than 3% is achieved for output signals up to 400 ke<sup>-</sup> typically.

- 6. These values are inferred by design and not measured.

- 7. The quoted maximum frequencies assume a 20 pF load and that correlated double sampling is being implemented.

- 8. The quoted dark signal has the usual temperature dependence for inverted mode operation. For operation at high frame rates with short integration times, there will also be a component generated during readout through the register. Operating at a temperature of 293 K and 10 Hz frame rate, the readout component contributes 5.8 e<sup>-</sup>/pixel/frame typically, at a gain of 1000 and referenced to the image area, and has a temperature dependence consistent with non-inverted mode operation.

There exists a further weakly temperature dependent component, the clock induced charge, which is independent of the integration time. The clock induced charge is dependent on the operating biases and timings employed and is typically 0.2 e<sup>-</sup>/ pixel/frame at T = -55 °C.

For more information, refer to the technical note "Dark Signal and Clock-Induced Charge in L3Vision<sup>TM</sup> CCD Sensors".

- 9. DSNU is defined as the  $1\sigma$  variation of the dark signal.

- 10. The excess noise factor is defined as the factor by which the multiplication process increases the shot noise on the image when multiplication gain is used.

#### **DEVICE COSMETIC PERFORMANCE**

Grade 1 devices are supplied to the blemish specification shown below. Note that incorrect biasing of the device may result in spurious dark or white blemishes appearing. These will be eliminated if the biases are adjusted.

#### **Test Conditions**

| Operating mode      | Devices run in 2-phase inverted mode, with an integration time of 100 ms and a readout rate of 15 MHz. |

|---------------------|--------------------------------------------------------------------------------------------------------|

| Sensor temperature  | $18 \pm 3 ^{\circ}\text{C}.$                                                                           |

| Multiplication gain | Set to approximately 1000.                                                                             |

| Illumination        | Set to give a signal level of approximately 60 e <sup>-</sup> /pixel/frame.                            |

#### **BLEMISH SPECIFICATION**

| Black Columns    | Black defects are counted when they have a responsivity of less than 80% of the local mean signal at approximately the specified multiplication gain and level of illumination. A black column contains at least 9 contiguous black defects.                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| White Columns    | White defects are pixels having a dark signal generation rate corresponding to an output signal of greater than 5 times the maximum specified dark signal level. A white column contains at least 9 contiguous white defects.                                                                                                                                                                                                        |

| Pin-Head Columns | Pin-head columns are manifest as a partial dark column with a bright pixel showing photoresponse<br>at the end of the column nearest to the readout register. Pin-head columns are counted when the<br>black column has a responsivity of less than 80% of the local mean signal at approximately the<br>specified multiplication gain and level of illumination. A pin-head column contains at least 9<br>contiguous black defects. |

#### SPECIFICATION

| PARAMETER                | GRADE 1 SPECIFICATION | GRADE 2 SPECIFICATION |

|--------------------------|-----------------------|-----------------------|

| White Columns            | 0                     | 0                     |

| Black / Pin-head Columns | 1                     | 6                     |

#### **ORDERING INFORMATION**

| PART NUMBER      | OPERATING MODE | COATING | WINDOW    |  |

|------------------|----------------|---------|-----------|--|

| CCD201-20-*- 122 | 2-phase        | Midband | Temporary |  |

\* denotes grade of device.

# Figure 1: TYPICAL VARIATION OF MULTIPLICATION GAIN WITH $R \statistical Different TEMPERATURES$

Figure 2: TYPICAL VARIATION OF DARK SIGNAL WITH TEMPERATURE

#### **ESD HANDLING PROCEDURES**

CCD sensors, in common with most high performance IC devices, are static sensitive. In certain cases a static electricity discharge may destroy or irreversibly degrade the device. Accordingly, full anti-static handling precautions should be taken whenever using a CCD sensor or module. These include:

- Working at a fully grounded workbench.

- Operator wearing a grounded wrist strap.

- All receiving socket pins to be positively grounded.

- Unattended CCDs should not be left out of their conducting foam or socket.

All devices are provided with internal protection circuits to most gate electrodes but not to the other pins.

Evidence of incorrect handling will terminate the warranty.

#### **EXPOSURE TO RADIATION**

Exposure to radiation may irreversibly damage the device and result in degradation of performance. Users wishing to operate the device in a radiation environment are advised to consult e2v technologies.

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum ratings are with respect to SS.

| PIN | CONNECTION | DESCRIPTION                                | MIN (V) | MAX (V) |

|-----|------------|--------------------------------------------|---------|---------|

| 1   | ABD        | Anti-blooming Drain (see note 11)          | -0.3    | + 25    |

| 2   | SS         | Substrate                                  |         | 0       |

| 3   | IØ4        | Image Clock 4                              | - 20    | + 20    |

| 4   | IØ3        | Image Clock 3                              | -20     | + 20    |

| 5   | SØ4        | Store Clock 4                              | -20     | + 20    |

| 6   | SØ2        | Store Clock 2                              | -20     | + 20    |

| 7   | SS         | Substrate                                  |         | 0       |

| 8   | SS         | Substrate                                  |         | 0       |

| 9   | DG         | Dump Gate                                  | -20     | + 20    |

| 10  | OG         | Output Gate                                | - 20    | + 20    |

| 11  | ODH        | Output Drain (HR Amplifier)                | -0.3    | + 32    |

| 12  | RD         | Reset Drain                                | -0.3    | + 25    |

| 13  | ODL        | Output Drain (LS Amplifier)                | -0.3    | + 32    |

| 14  | SS         | Substrate                                  |         | 0       |

| 15  | OSH        | Output Source (HR Amplifier) (see note 12) | -0.3    | + 25    |

| 16  | OSL        | Output Source (LS Amplifier) (see note 12) | -0.3    | + 25    |

| 17  | ØR         | Reset Pulse                                | -20     | + 20    |

| 18  | RØDC       | Multiplication Register DC Bias            | -20     | + 20    |

| 19  | RØ2HV      | Multiplication Register Clock              | -20     | + 50    |

| 20  | DG         | Dump Gate                                  | -20     | + 20    |

| 21  | n.c.       | Not Connected                              |         |         |

| 22  | n.c.       | Not Connected                              |         |         |

| 23  | SS         | Substrate                                  |         | 0       |

| 24  | n.c.       | Not Connected                              |         |         |

| 25  | n.c.       | Not Connected                              |         |         |

| 26  | DD         | Dump Drain                                 | -0.3    | + 25    |

| 27  | RØ3        | Register Clock 3                           | -20     | + 20    |

| 28  | RØ1        | Register Clock 1                           | -20     | + 20    |

| 29  | RØ2        | Register Clock 2                           | -20     | + 20    |

| 30  | SS         | Substrate                                  |         | 0       |

| 31  | SØ3        | Store Clock 3                              | -20     | + 20    |

| 32  | SØ1        | Store Clock 1                              | -20     | + 20    |

| 33  | IØ1        | Image Clock 1                              | -20     | + 20    |

| 34  | IØ2        | Image Clock 2                              | -20     | + 20    |

| 35  | SS         | Substrate                                  |         | 0       |

| 36  | IG         | Isolation Gate                             | -20     | + 20    |

#### NOTES

11. Anti-blooming is not available on this device type. However, ABD is used for connection purposes and must be biased as specified.

12. Permanent damage may result if, in operation, OSL or OSH experience short-circuit conditions.

#### Maximum voltages between pairs of pins:

| PIN  | CONNECTION           | PIN | CONNECTION | MIN<br>(V) | MAX<br>(V) |

|------|----------------------|-----|------------|------------|------------|

| 15   | OSH                  | 11  | ODH        | - 15       | + 15       |

| 16   | OSL                  | 13  | ODL        | — 15       | + 15       |

| 19   | RØ2HV                | 18  | RØDC       | -20        | + 50       |

| 19   | RØ2HV                | 27  | RØ3        | -20        | + 50       |

| Outp | out transistor curre |     | 20         |            |            |

#### **OPERATING CONDITIONS**

Typical operating voltages are as given in the table below. Some adjustment within the minimum-maximum range specified may be required to optimise performance.

| CONNECTION     | PULSE AMPLITUDE OR DC LEVEL (V) |         |                  |  |  |  |  |  |

|----------------|---------------------------------|---------|------------------|--|--|--|--|--|

|                | Min                             | Typical | Мах              |  |  |  |  |  |

| IØ1,2,3,4 high | +5 (see note 13)                | +7      | +9 (see note 13) |  |  |  |  |  |

| IØ1,2,3,4 low  | -6                              | -5      | -4               |  |  |  |  |  |

| SØ1,2,3,4 high | +5 (see note 13)                | +7      | +9 (see note 13) |  |  |  |  |  |

| SØ1,2,3,4 low  | -6                              | -5      | -4               |  |  |  |  |  |

| RØ1,2,3 high   | +8                              | + 12    | + 13             |  |  |  |  |  |

| RØ1,2,3 low    | -                               | 0       | -                |  |  |  |  |  |

| RØ2HV high     | + 20                            | + 40    | +50 (see note 4) |  |  |  |  |  |

| RØ2HV low      | 0                               | +4      | +5               |  |  |  |  |  |

| ØR high        | see note 14                     | + 10    | see note 14      |  |  |  |  |  |

| ØR low         | -                               | 0       | -                |  |  |  |  |  |

| RØDC           | +2                              | +3      | +5               |  |  |  |  |  |

| OG             | + 1                             | +3      | +5               |  |  |  |  |  |

| IG             | -                               | -5      | -                |  |  |  |  |  |

| SS             | 0                               | +4.5    | +7               |  |  |  |  |  |

| ODL, ODH       | + 25                            | + 28    | + 32             |  |  |  |  |  |

| RD             | + 15                            | + 17    | + 20             |  |  |  |  |  |

| ABD            | + 10                            | + 18    | + 20             |  |  |  |  |  |

| DG low         | -                               | 0       | -                |  |  |  |  |  |

| DG high        | + 10                            | + 12    | + 13             |  |  |  |  |  |

| DD             | + 20                            | + 24    | + 25             |  |  |  |  |  |

#### NOTES

13. I $\emptyset$  and S $\emptyset$  adjustment may be common.

14.  $\emptyset$ R high level may be adjusted in common with R $\emptyset$ 1,2,3.

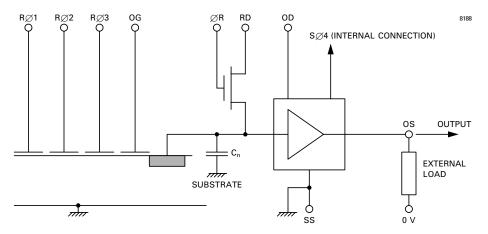

15. Between the two amplifiers, common connections are made to the reset gates (ØR), reset drains (RD) and output gates (OG).

16. An external load is required for each output amplifier. For the HR amplifier, this can be a resistor of about 5 k $\Omega$  (non-critical) or a constant current type of about 5 mA. For the LS amplifier, the load should be either 3.3 k $\Omega$  or 7.5 mA. The on-chip amplifier power dissipation is approximately 30 mW for the HR amplifier and 50 mW for the LS amplifier.

#### DRIVE PULSE WAVEFORM SPECIFICATION

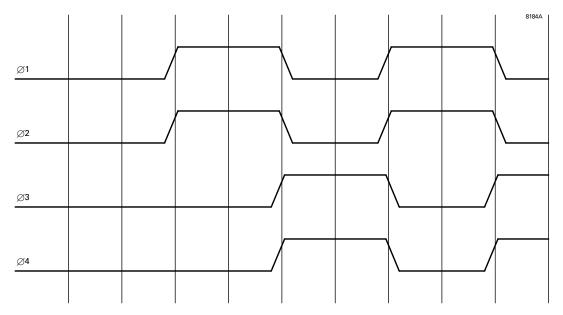

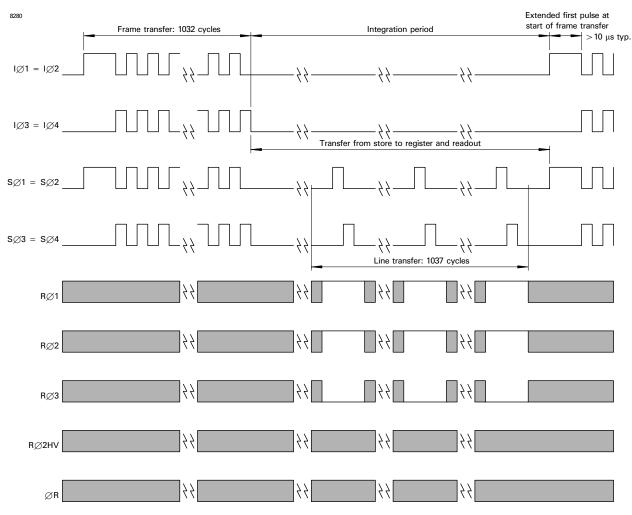

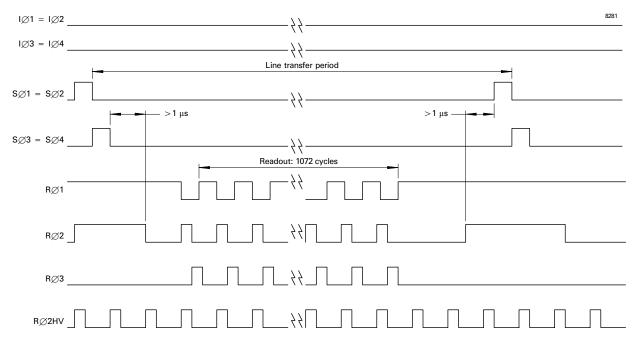

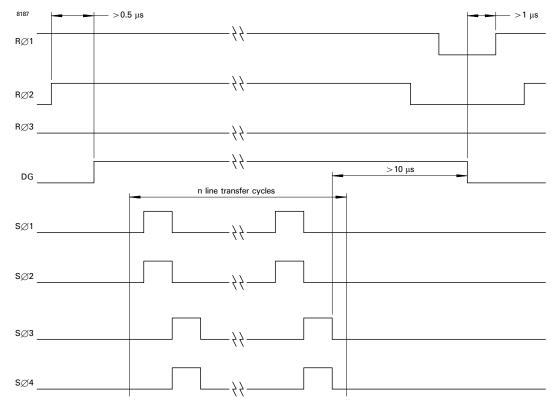

The device is of a 4-phase construction, designed to operate in 2-phase inverted mode. This is achieved by applying common timings to phases  $\emptyset$ 1 and  $\emptyset$ 2, and phases  $\emptyset$ 3 and  $\emptyset$ 4 of the image and store sections. Suggested timing diagrams are shown in Figs. 4 - 11. The following are suggested pulse rise and fall times.

| CLOCK PULSE | TYPICAL RISE TIME $\tau$ (ns) | TYPICAL FALL TIME $\tau$ (ns) | TYPICAL PULSE OVERLAP                             |

|-------------|-------------------------------|-------------------------------|---------------------------------------------------|

| IØ          | $140 < \tau < 200$            | $140 < \tau < 200$            | @90% points                                       |

| SØ          | $140 < \tau < 200$            | $140 < \tau < 200$            | @90% points                                       |

| RØ1         | 10                            | 10                            | @70% points                                       |

| RØ2         | 10                            | 10                            | @70% points                                       |

| RØ3         | 10                            | 10                            | @70% points                                       |

| RØ2HV       | 25                            | 25                            | see note 18                                       |

| RØ2HV       | Sine                          | Sine                          | Sinusoid- high on falling edge of $R \emptyset 1$ |

#### NOTES

17. Register clock pulses are as shown in Figs. 5 and 6.

18. An example clocking scheme is shown in Fig. 5. RØ2HV can also be operated with a normal clock pulse, as shown in Fig. 6. The requirement for successful clocking is that RØ2HV reaches its maximum amplitude before RØ1 goes low.

| Connection                  | Capacitance to SS                   | Inter-phase Capacitances | Total Capacitance | Units |

|-----------------------------|-------------------------------------|--------------------------|-------------------|-------|

| IØ1                         | 2.4                                 | 2.4                      | 7.2               | nF    |

| IØ2                         | 5.4                                 | 2.4                      | 10.2              | nF    |

| IØ3                         | 2.4                                 | 2.4                      | 7.2               | nF    |

| IØ4                         | 5.4                                 | 2.4                      | 10.2              | nF    |

| SØ1                         | 2.4                                 | 2.4                      | 7.2               | nF    |

| SØ2                         | 5.4                                 | 2.4                      | 10.2              | nF    |

| SØ3                         | 2.4                                 | 2.4                      | 7.2               | nF    |

| SØ4                         | 5.4                                 | 2.4                      | 10.2              | nF    |

| RØ1                         | 68                                  | 98                       | 166               | рF    |

| RØ2                         | 56                                  | 68                       | 124               | рF    |

| RØ3                         | 89                                  | 74                       | 163               | рF    |

| RØ2HV                       | 15                                  | 18                       | 33                | рF    |

| SERIES RESISTANCES          |                                     |                          |                   |       |

| Connection                  | Approximate Total Series Resistance |                          |                   |       |

| IØ1                         | 16                                  |                          |                   | Ω     |

| IØ2                         |                                     | 14                       |                   | Ω     |

| IØ3                         |                                     | 16                       |                   | Ω     |

| IØ4                         |                                     | 14                       |                   | Ω     |

| SØ1                         |                                     | 16                       |                   | Ω     |

| SØ2                         |                                     | 14                       |                   | Ω     |

| SØ3                         |                                     | 16                       |                   | Ω     |

| SØ4                         | 14                                  |                          |                   | Ω     |

| RØ1                         | 6                                   |                          |                   | Ω     |

| RØ2                         | 6                                   |                          |                   | Ω     |

| RØ3                         |                                     | 6                        |                   | Ω     |

| RØ2HV                       |                                     | 8                        |                   | Ω     |

| APPROXIMATE OUTPUT I        | MPEDANCE                            |                          |                   |       |

| Large Signal Amplifier      | 350                                 |                          |                   | Ω     |

| High Responsivity Amplifier |                                     | 400                      |                   | Ω     |

#### PULSE TIMINGS AND OVERLAPS

#### Figure 4: CLOCKING SCHEME FOR 2-PHASE INVERTED MODE OPERATION

# Figure 5: CLOCKING SCHEME FOR MULTIPLICATION GAIN (Sine wave clocking scheme) (see note 19)

Figure 6: CLOCKING SCHEME FOR MULTIPLICATION GAIN (Conventional clocking scheme) (see note 19)

#### NOTE

19. To operate through the OSH output amplifier, the RØ1 and RØ2 waveforms should be interchanged.

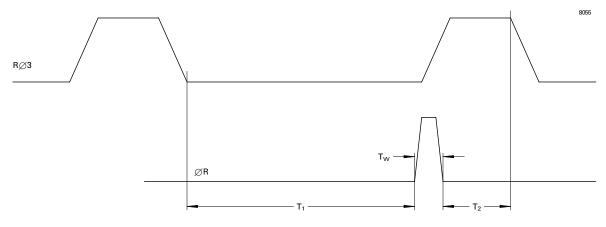

#### Figure 7: RESET PULSE

$T_W = 10 \text{ ns typical}$   $T_1 = \text{output valid}$  $T_2 > 0 \text{ ns}$

#### Figure 9: EXAMPLE FRAME TIMING DIAGRAM

Figure 10: EXAMPLE LINE TIMING DIAGRAM (Operation through OSL, see notes 19 and 22)

# Figure 11: OPERATION OF THE DUMP GATE TO DUMP n LINES OF UNWANTED DATA FROM THE STANDARD REGISTER

#### NOTE

20. Wanted lines of data must be completely read out before dumping unwanted data.

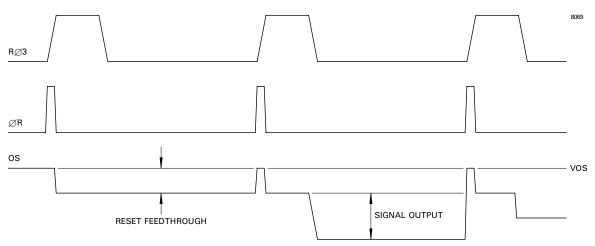

#### Figure 12: OUTPUT CIRCUIT SCHEMATIC (OSL and OSH Amplifiers)

#### NOTE

21. The amplifiers have a DC restoration circuit that is internally activated whenever SØ4 is high.

#### Figure 13: SCHEMATIC CHIP DIAGRAM

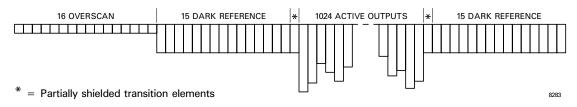

#### Figure 14: LINE OUTPUT FORMAT (for Example Line Timing Figure 10)

#### NOTE

22. There is a 1-line propagation delay between transferring a line from the store section to the standard register and reading it out through the OSL output amplifier.

#### Figure 15: PACKAGE OUTLINE

#### **Outline Note**

The image centre is aligned centrally in the package in direction 'X', to within a tolerance of  $\pm 0.2$  mm.

Whilst e2v technologies has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. e2v technologies accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.